Vous ne mourrez pas, ordonne l’industrie des puces, pour que la loi de Moore reste vivante. Voilà une tâche difficile. Le PDG d’Imec explique quelles nouvelles technologies sont nécessaires pour continuer à développer les puces afin de disposer d’une puissance de calcul suffisante pour soutenir la numérisation de notre société à l’avenir.

Jésus serait jaloux de la loi de Moore : rien ni personne n’est mort et ressuscité plus que la prédiction de Gorden Moore, cofondateur d’Intel, qui a établi dès 1965 que le nombre de transistors sur un microcircuit doublerait environ tous les deux ans.

Doublement obligatoire

La loi de Moore ressemble presque à une loi de la physique, mais on peut en fait l’interpréter comme une règle juridique. La densité des transistors ne doublera pas, elle le doit. La prédiction de Moore survit par la grâce d’une collection internationale d’ingénieurs ayant un QI digne de Mensa et des milliards de dollars en recherche et développement. La sanction pour ceux qui ne se conforment pas ? Un coup dur pour leur réputation, mais surtout une position concurrentielle plus faible face aux fabricants de puces qui sont parvenus à suivre le rythme infernal de l’innovation. Demandez à GlobalFoundries. À qui ? Exactement.

Luc Van den hove, PDG d’Imec, est l’un des protagonistes de Moore. « La loi ne peut pas s’arrêter et ne s’arrêtera pas », a-t-il déclaré en mai sur la scène des Imec Future Summits 2022. « Pratiquement toutes les applications, dans tous les domaines, vont nécessiter d’énormes capacités de données », prédit-il. Van den hove cite entre autres le secteur médical, mais comme tout le monde, il voit la tendance à la numérisation au-delà des frontières sectorielles. « Afin de piloter ces changements, nous avons besoin d’une technologie des semi-conducteurs performante. »

Moore vs la physique

C’est plus vite dit que fait. Lorsque la loi de Moore entre en conflit avec les lois de la physique, tout progrès tend à s’arrêter. Les structures individuelles des micropuces et certainement des transistors approchent de la taille des atomes, où les effets quantiques commencent à interférer avec le fonctionnement des micropuces. En outre, même les meilleurs équipements du monde sont presque trop lourds pour appliquer ces structures atomiques aux tranches de silicium. Quelque chose doit changer, et ce ne sera pas la physique quantique.

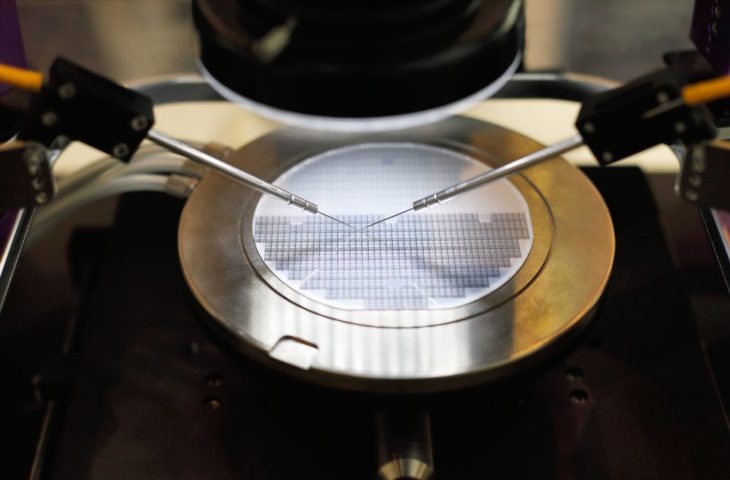

« L’échelonnage traditionnel trouve aujourd’hui ses limites », constate Van den hove lui-même. « Et la lithographie pure le fait certainement. » La lithographie est le processus par lequel une machine projette de la lumière à travers une sorte de stencil sur une plaquette. Là où la lumière pénètre, elle réagit avec les produits chimiques de la plaquette et ainsi, couche après couche, modèle après modèle, les micropuces sont construites. Le problème : la lithographie traditionnelle utilise la lumière, et la longueur d’onde de la lumière est supérieure à la précision requise des stencils. Tentez de copier un Rubens avec un rouleau à peinture…

Van den hove voit toute une série de solutions. En tant qu’institut de R&D de réputation internationale, l’Imec est en excellente position pour considérer ces problèmes comme des défis. Elle travaille en collaboration avec, entre autres, ASML, qui construit les machines de lithographie les plus avancées au monde, pour trouver des réponses.

Du rouleau de peinture au pinceau

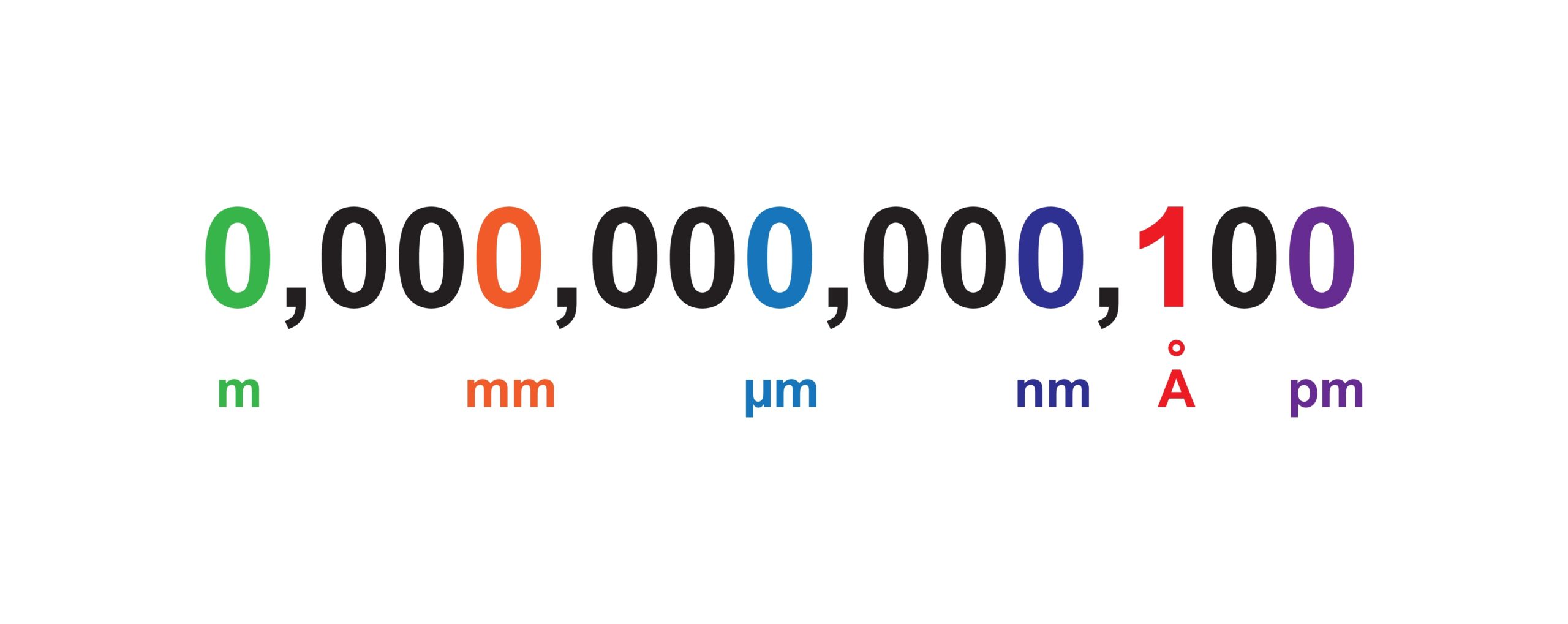

Une solution : des pinceaux plus fins. La longueur d’onde de la lumière visible est-elle trop grande ? Alors, la lumière invisible. La lithographie avec l’UV extrême (EUV) est complexe, mais elle figure de plus en plus dans les chaînes de production fonctionnelles. « L’EUV nous fera passer de 5 nm à 2 nm », prédit Van den hove. Mais cela ne suffit pas. Pour réduire la taille de l’appareil, nous avons besoin d’une nouvelle version de l’EUV avec des objectifs différents. Le diamètre sera de 1 mètre et la précision de 20 picomètres.

Un non-initié a du mal à l’imaginer, alors Van den hove précise : « Si nous extrapolons cela au niveau de la terre, nous devons polir le globe avec une déviation d’une épaisseur d’un cheveu humain au maximum. » Cependant, il ne semble pas s’inquiéter. En collaboration avec ASML, l’Imec espère que la technologie High-NA EUV sera prête à temps.

Nouveaux défis à relever

Passons à de nouveaux problèmes. « Pratiquement tous les gains de performance, de densité et de coût sont venus de la réduction de la taille d’un seul composant : le transistor. » Selon Van den hove, les transistors sont aujourd’hui si petits que la conception des puces se heurte à un nouveau défi. Ou plutôt : de nouveaux défis. « La bande passante de la mémoire n’arrive pas à suivre les performances de l’unité centrale », sait-il. Le processeur ne peut pas travailler plus vite que les données et les instructions disponibles en mémoire. C’est le défi de la mémoire. « En outre, il devient plus difficile de faire entrer suffisamment de puissance dans la puce, mais aussi d’évacuer la chaleur. Le refroidissement ne peut pas suivre. » Voilà le défi d’électricité.

Il est plus difficile de transmettre suffisamment de puissance dans la puce, mais aussi d’évacuer la chaleur.

Luc Van den hove, PDG de l’Imec

Van den hove veut faire disparaître ces défis. C’est nécessaire si Moore veut garder la vie sauve. Une solution pour le défi de l’électricité est déjà prévue. « La distribution électrique s’étend désormais du sommet de la plaquette au transistor, en passant par plus de dix couches. Il faut changer cela en arrière. Nous allons enfoncer des rails d’alimentation dans la plaquette. » C’est ce qu’on appelle des Nano-through-Silicon-vias. La technologie est complexe, mais le principe est simple : il faut d’abord construire un squelette pour l’alimentation électrique, avec les transistors par-dessus. Cela donne plus de flexibilité aux interconnexions qui se trouvent au-dessus des transistors et les relient en circuits logiques, et rend l’ensemble plus efficace.

Pour faire tomber le défi de la mémoire, la mémoire doit se rapprocher de la puce. Van den hove étudie les structures 3D sur les interposeurs avec des connexions directes en silicium aux blocs DRAM. Les puces doivent être emballées avec la mémoire dans un paquet 3D. En outre, il voit un rôle pour les interconnexions optiques.

Nouveaux transistors

Le chemin est encore long, mais la feuille de route est déjà en place. L’Imec a préparé une feuille de route qui nous mène de 2018 et 7 nm à 2036 et 0,2 nm ou 2 angströms. L’EUV et l’EUV H-NA jouent un rôle majeur à cet égard, tout comme les conceptions 3D plus complexes et, bien sûr, les nouvelles conceptions des transistors eux-mêmes.

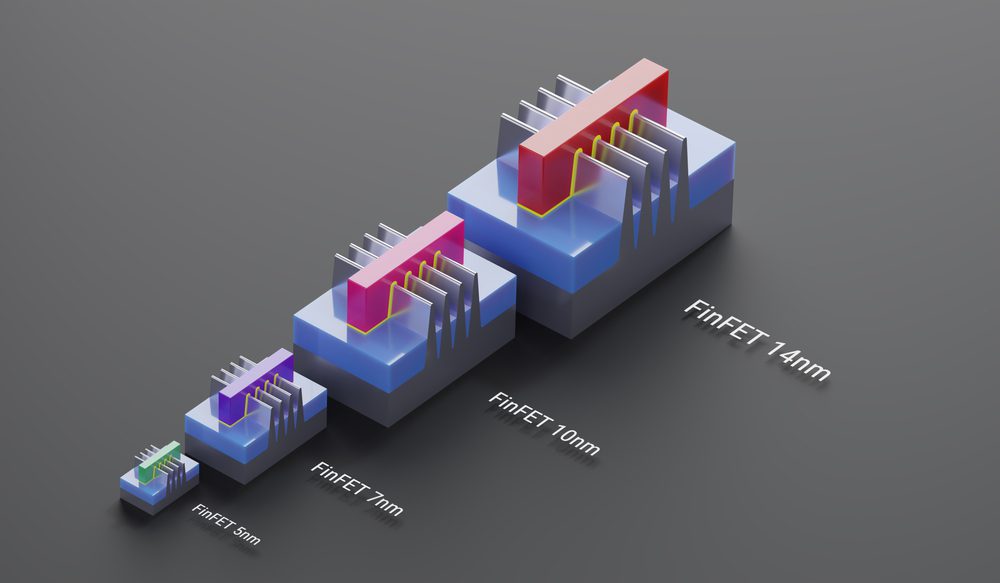

La plupart des fabricants de puces fabriquent aujourd’hui des puces avec des transistors FinFET, mais cette conception souffre trop des interférences quantiques. Samsung vient de lancer la production de puces avec son successeur : le transistor Gate-All-Around (GAA) ou nanosheet. Selon Van den hove, cela sera essentiel à partir de 2 nm. TSMC et Intel sont d’accord, et continueront à travailler avec FinFET pour les puces de 3 nm.

Bien que le transistor GAA soit déjà à la pointe de la technologie, Imec et Van den hove anticipent l’avenir. Un successeur est déjà bien préparé : le transistor CFET. Il s’agit d’une utilisation optimale des trois dimensions et d’un successeur vertical complexe de la GAA. En temps voulu, Van den hove s’attend à ce que les produits à puce intègrent de nouveaux matériaux monocouches 2D ultrafins d’une épaisseur atomique. En d’autres termes, à l’Imec, on sait ce qu’il faut faire ensuite.

Moore survit, Von Neumann doit mourir

À long terme, selon Van den hove, l’architecture Von Neumann devra être revue. Cette évolution est déjà visible. Von Neumann voyait l’ordinateur numérique comme un système avec des entrées, une unité centrale de traitement et des sorties. « Nous devons évoluer vers des architectures spécifiques à un domaine », prévoit Van den hove, « comme le cerveau fonctionne ».

Cela implique que l’unité centrale jouera un rôle de plus en plus réduit au profit de circuits personnalisés pour des charges de travail spécifiques. « Si nous suivons cette vision, la loi de Moore ne s’arrêtera pas », prévoit le PDG de l’Imec. Von Neumann est sacrifié pour garder Moore parmi les vivants.

Du nanomètre au ångström en 14 ans

Concrètement, qu’est-ce que cela signifie ? Pour le 3 nm, nous sommes sur la bonne voie : l’Imec prévoit une production en volume de ce produit cette année, et Samsung a déjà donné le ton. TSMC suivra bientôt. D’ici à 2024, les premières puces de 2 nm devraient sortir de la bande avec des transistors GAA Nanosheet. À partir de 2026, nous pourrons alors mesurer en ångström (Å) à 1,4 nm ou 14 Å.

D’ici à 2030, nous baisserons vraiment en dessous de 1 nm avec 7 Å et la GAA arrivera à ses limites. La voie de la science-fiction s’ouvre en 2032 avec 5 Å et CFET, avec une trajectoire vers 3 Å et 2036 avec des matériaux et des interconnexions à l’échelle atomique. Est-ce que c’est optimiste ? Peut-être. Quoi qu’il en soit, le passage de 14 nm à 10 nm a pris plus de temps que prévu, notamment en raison de la difficulté de mise en œuvre de l’EUV. Entre-temps, le wagon de la miniaturisation semble être à nouveau dans la phase de croisière.

Duidelijke landkaart

Le principal fait est que les constructeurs de puces n’ont pas l’ombre d’un doute. Il y a un chemin clair vers la compression. Le transistor peut diminuer un peu, les conceptions peuvent devenir plus efficaces en termes de flux de courant et la mémoire peut se rapprocher de la puce. C’est difficile, mais si nous devons croire Van den Hove, cela ne devrait pas être un problème. Difficile signifie aussi possible, et Moore doit être défendu. La réussite de la numérisation de la société en dépend.